The First Monolithic 3D Chip Built in a U.S. Foundry Promises a Major Leap in AI Performance

A major milestone has just been reached in semiconductor research, and it could significantly reshape how future AI hardware is designed and manufactured. A collaborative team of engineers and researchers from Stanford University, Carnegie Mellon University, the University of Pennsylvania, and MIT, working alongside SkyWater Technology, has successfully built the first monolithic 3D integrated circuit fabricated in a commercial U.S. foundry. Even more impressive, this chip doesn’t just exist as a proof of concept—it delivers order-of-magnitude performance gains over conventional 2D chips in both real hardware tests and simulations.

At a time when artificial intelligence systems are demanding ever-increasing computational power, this development points toward a practical path beyond the physical limits that have constrained chip design for years.

Why Today’s Chips Are Struggling to Keep Up With AI

Modern AI models rely on enormous volumes of data constantly moving between memory and computing units. While processors have become extremely fast, the movement of data has not kept pace. This mismatch creates what engineers call the memory wall—a bottleneck where processors sit idle, waiting for data to arrive.

For decades, the semiconductor industry pushed past such limitations by shrinking transistors and packing more of them onto a chip. That strategy, often referred to as Moore’s Law scaling, is now running into unavoidable physical limits, sometimes described as the miniaturization wall. Transistors can only get so small before heat, leakage, and manufacturing complexity become unmanageable.

This is where a new architectural approach becomes necessary.

What Makes This Chip Different From Traditional Designs

Unlike conventional flat, 2D chips, the new prototype is built vertically. Instead of spreading components across a single plane, the researchers stacked ultra-thin layers of memory and logic directly on top of one another, forming a tightly integrated three-dimensional structure.

The key idea is simple but powerful: when memory and computing elements are physically closer, data doesn’t need to travel long distances. The chip uses extremely dense vertical interconnects, allowing information to move up and down between layers rapidly, much like high-speed elevators in a skyscraper.

This vertical integration dramatically reduces data transfer delays, alleviating the memory wall that has slowed progress in AI accelerators for years.

Monolithic 3D Integration Versus Chip Stacking

Many existing 3D chip approaches rely on stacking separate chips on top of each other after fabrication. While effective to a degree, these methods suffer from limited and coarse connections between layers, which can still become bottlenecks.

The breakthrough here lies in the monolithic fabrication process. Instead of building layers separately and bonding them later, each layer of this chip is fabricated sequentially on the same wafer, in a single continuous process. This allows for far denser vertical wiring and much tighter integration between logic and memory.

Crucially, the team achieved this using low-temperature processing techniques, ensuring that newly built layers do not damage the circuitry underneath.

Built Entirely in a U.S. Commercial Foundry

One of the most significant aspects of this achievement is where it was made. The entire chip was fabricated at SkyWater Technology, the largest exclusively U.S.-based pure-play semiconductor foundry. Previous monolithic 3D chips existed only as academic lab experiments. This is the first time such a design has demonstrated clear performance benefits while being manufactured in a commercial fabrication facility.

This proves that advanced monolithic 3D architectures are not just theoretical or experimental—they are manufacturable at scale using existing U.S. semiconductor infrastructure.

Measured Performance Gains and AI Workloads

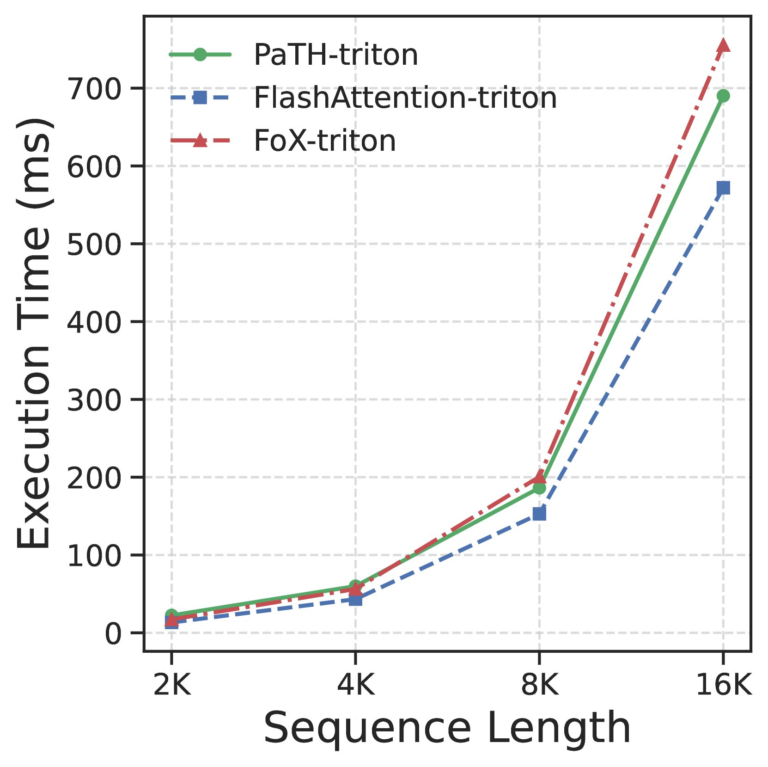

Early hardware measurements already show strong improvements. The prototype delivers roughly four times the performance of comparable 2D chips built using similar technology nodes.

The researchers also ran extensive simulations of taller chip designs, adding more stacked layers of memory and compute units. These simulations point to even larger gains, with up to 12× performance improvements on realistic AI workloads. Some of these workloads were derived from Meta’s open-source LLaMA large language model, making the results especially relevant for modern AI applications.

Perhaps most striking is the projected improvement in energy-delay product (EDP), a key metric that balances speed and energy efficiency. The team estimates that future versions of this architecture could achieve 100× to 1,000× improvements in EDP compared to traditional flat chips.

Inside the Chip: Materials and Manufacturing Details

Technically, the chip combines several advanced components into a single vertically integrated structure. These include standard CMOS logic, resistive RAM (RRAM) for dense memory storage, and carbon nanotube field-effect transistors (CNFETs), which are well-suited for low-temperature fabrication.

The prototype was produced using a mature manufacturing node on 200 mm wafers, showing that cutting-edge performance gains are possible even without bleeding-edge lithography. This is an important point, as it suggests monolithic 3D integration could extend the useful life of existing fabrication processes.

Why This Matters for the Future of AI Hardware

AI systems are rapidly approaching the limits of what conventional architectures can support. Training and running large models increasingly depends on data movement efficiency, not just raw compute power.

By tightly integrating memory and logic in three dimensions, monolithic 3D chips offer a practical solution to both the memory wall and the miniaturization wall. Shorter data paths mean higher throughput, lower latency, and reduced energy consumption—a combination that has long been considered extremely difficult to achieve.

This approach also opens the door to domain-specific AI accelerators, where memory and computation are customized for particular workloads, such as deep learning, scientific computing, or edge AI.

Strategic Importance for U.S. Semiconductor Leadership

Beyond performance, this work carries broader strategic significance. Demonstrating that advanced 3D chips can be built entirely within the United States strengthens domestic semiconductor capabilities at a critical time.

Just as earlier generations of U.S.-trained engineers helped drive the integrated circuit revolution, the shift toward vertical, monolithic 3D integration will require a new workforce skilled in these technologies. Through collaborations, funding programs, and hands-on fabrication experience, students and researchers are already being trained to lead this next phase of innovation.

Looking Ahead

While this chip is still a prototype, it establishes a clear and realistic roadmap for future AI hardware. As more layers are added and designs are refined, the performance gains could scale dramatically. More importantly, this research shows that monolithic 3D integration is not just an academic curiosity—it is a viable path forward for the semiconductor industry.

In a world where AI progress increasingly depends on hardware breakthroughs, this development marks a pivotal step toward faster, more efficient, and domestically produced computing systems.

Research paper:

https://ieeexplore.ieee.org/document/IEDM2025-monolithic-3D-chip